# **ESP32-PICO-D4** Datasheet

Version 1.2

Espressif Systems

## **About This Guide**

This document provides an introduction to the specifications of the ESP32-PICO-D4 module.

### **Revision History**

For revision history of this document, please refer to the last page.

### **Documentation Change Notification**

Espressif provides email notifications to keep customers updated on changes to technical documentation. Please subscribe here.

### Certification

Download certificates for Espressif products from here.

### **Disclaimer and Copyright Notice**

Information in this document, including URL references, is subject to change without notice. THIS DOCUMENT IS PROVIDED AS IS WITH NO WARRANTIES WHATSOEVER, INCLUDING ANY WARRANTY OF MERCHANTABIL-ITY, NON-INFRINGEMENT, FITNESS FOR ANY PARTICULAR PURPOSE, OR ANY WARRANTY OTHERWISE ARISING OUT OF ANY PROPOSAL, SPECIFICATION OR SAMPLE.

All liability, including liability for infringement of any proprietary rights, relating to use of information in this document is disclaimed. No licenses express or implied, by estoppel or otherwise, to any intellectual property rights are granted herein. The Wi-Fi Alliance Member logo is a trademark of the Wi-Fi Alliance. The Bluetooth logo is a registered trademark of Bluetooth SIG.

All trade names, trademarks and registered trademarks mentioned in this document are property of their respective owners, and are hereby acknowledged.

Copyright © 2018 Espressif Inc. All rights reserved.

## Contents

| 1                                           | Overview                                                                  | 1                           |

|---------------------------------------------|---------------------------------------------------------------------------|-----------------------------|

| <b>2</b><br>2.1<br>2.2<br>2.3               |                                                                           | 3<br>3<br>3<br>5            |

| <b>3</b><br>3.1<br>3.2<br>3.3<br>3.4<br>3.5 | External Flash and SRAM<br>Crystal Oscillators<br>Peripherals and Sensors | 7<br>7<br>7<br>7<br>8<br>12 |

| <b>4</b><br>4.1<br>4.2<br>4.3               | Wi-Fi Radio                                                               | 14<br>14<br>15<br>15<br>15  |

| 5                                           | Schematics                                                                | 17                          |

| 6<br>7                                      | Peripheral Schematics<br>Package Information                              | 18                          |

| <b>8</b><br>8.1<br>8.2                      | Learning Resources<br>Must-Read Documents                                 | 20<br>20<br>20              |

| Re                                          | evision History                                                           | 21                          |

## List of Tables

| 1 | ESP32-PICO-D4 Specifications           | 1  |

|---|----------------------------------------|----|

| 2 | Pin Description                        | 3  |

| 3 | Strapping Pins                         | 6  |

| 4 | Description of Peripherals and Sensors | 8  |

| 5 | Power Consumption by Power Modes       | 13 |

| 6 | Absolute Maximum Ratings               | 14 |

| 7 | Wi-Fi Radio Characteristics            | 14 |

| 8 | Receiver Characteristics – BLE         | 15 |

| 9 | Transmit Characteristics – BLE         | 15 |

## List of Figures

| 1 | ESP32-PICO-D4 Pin Layout                   | 3  |

|---|--------------------------------------------|----|

| 2 | ESP32-PICO-D4 Module Schematics            | 17 |

| 3 | ESP32-PICO-D4 Module Peripheral Schematics | 18 |

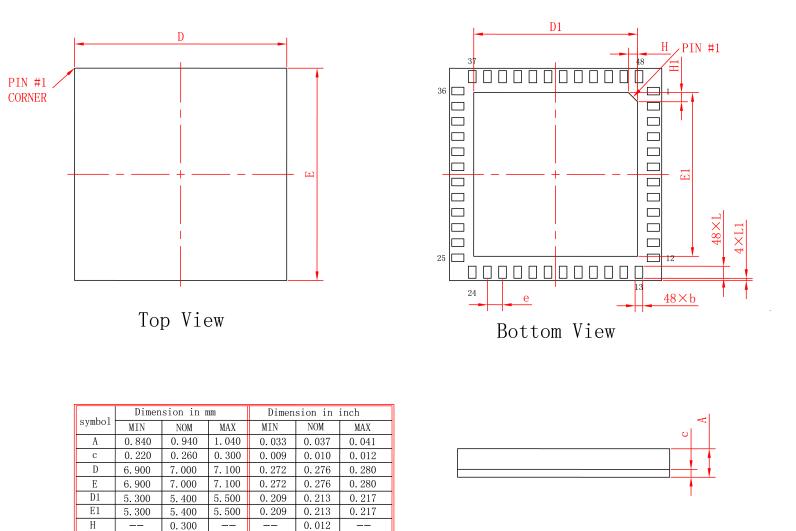

| 4 | ESP32-PICO-D4 Package                      | 19 |

## 1. Overview

The ESP32-PICO-D4 is a System-in-Package (SIP) module that is based on ESP32, providing complete Wi-Fi and Bluetooth functionalities. The module has a size as small as 7.0±0.1 mm×7.0±0.1 mm×0.94±0.1 mm, thus requiring minimal PCB area. The module integrates a 4-MB SPI flash.

At the core of this module is the ESP32 chip\*, which is a single 2.4 GHz Wi-Fi and Bluetooth combo chip designed with TSMC's 40 nm ultra-low power technology. ESP32-PICO-D4 integrates all peripheral components seamlessly, including a crystal oscillator, flash, filter capacitors and RF matching links in one single package. Given that no other peripheral components are involved, module welding and testing is not required either. As such, ESP32-PICO-D4 reduces the complexity of supply chain and improves control efficiency.

With its ultra-small size, robust performance and low-energy consumption, ESP32-PICO-D4 is well suited for any space-limited or battery-operated applications, such as wearable electronics, medical equipment, sensors and other IoT products.

Note:

\* For details on ESP32, please refer to the document ESP32 Datasheet.

Table 1 provides the specifications of the ESP32-PICO-D4 module.

| Categories | Items                          | Specifications                                               |

|------------|--------------------------------|--------------------------------------------------------------|

|            |                                | 802.11 b/g/n/e/i (802.11n up to 150 Mbps)                    |

| Wi-Fi      | Protocols                      | A-MPDU and A-MSDU aggregation and 0.4 $\mu$ s guard interval |

|            |                                | support                                                      |

|            | Frequency range                | 2.4 ~ 2.5 GHz                                                |

|            | Protocols                      | Bluetooth V4.2 BR/EDR and BLE specification                  |

|            |                                | NZIF receiver with -97 dBm sensitivity                       |

| Bluetooth  | Radio                          | Class-1, class-2 and class-3 transmitter                     |

|            |                                | AFH                                                          |

|            | Audio                          | CVSD and SBC                                                 |

|            |                                | ADC, LNA pre-amplifier, DAC, touch sensor, SD/SDIO/MMC       |

|            | Module interface               | Host Controller, SPI, SDIO/SPI Slave Controller, EMAC, mo-   |

|            |                                | tor PWM, LED PWM, UART, I2C, I2S, infrared remote con-       |

|            |                                | troller, GPIO                                                |

|            | On-chip sensor                 | Hall sensor, temperature sensor                              |

|            | On-board clock                 | 40 MHz crystal                                               |

| Hardware   | Operating voltage/Power supply | 2.7 ~ 3.6V                                                   |

|            | Operating current              | Average: 80 mA                                               |

|            | Minimum current delivered by   | 500 mA                                                       |

|            | power supply                   |                                                              |

|            | Operating temperature range    | -40°C ~ 85°C                                                 |

|            | Ambient temperature range      | Normal temperature                                           |

|            | Package size                   | 7.0±0.1 mm x 7.0±0.1 mm x 0.94±0.1 mm                        |

#### Table 1: ESP32-PICO-D4 Specifications

| Categories | Items                | Specifications                                        |  |

|------------|----------------------|-------------------------------------------------------|--|

|            | Wi-Fi mode           | Station/SoftAP/SoftAP+Station/P2P                     |  |

|            | Wi-Fi security       | WPA/WPA2/WPA2-Enterprise/WPS                          |  |

|            | Encryption           | AES/RSA/ECC/SHA                                       |  |

|            | Firmware upgrade     | UART Download / OTA (via network / download and write |  |

| Software   |                      | firmware via host)                                    |  |

|            | Software development | Supports Cloud Server Development / SDK for custom    |  |

|            |                      | firmware development                                  |  |

|            | Network protocols    | IPv4, IPv6, SSL, TCP/UDP/HTTP/FTP/MQTT                |  |

|            | User configuration   | AT instruction set, cloud server, Android/iOS app     |  |

## 2. Pin Definitions

### 2.1 Pin Layout

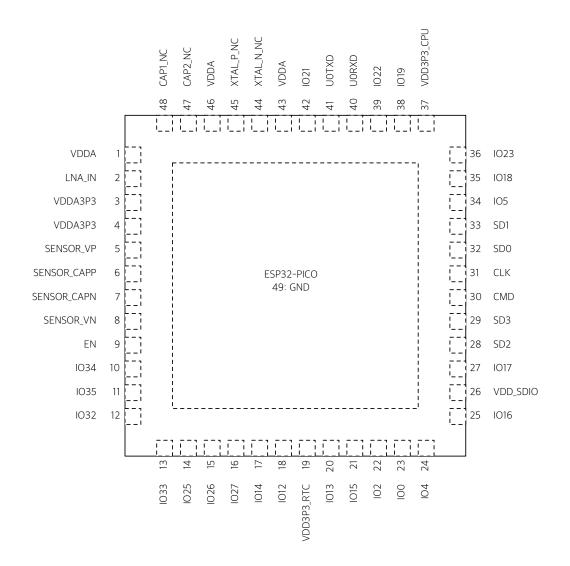

Figure 1: ESP32-PICO-D4 Pin Layout

### 2.2 Pin Description

The ESP32-PICO-D4 module has 48 pins. See pin definitions in Table 2.

#### Table 2: Pin Description

| Name    | No.                                             | Туре | Function                             |  |

|---------|-------------------------------------------------|------|--------------------------------------|--|

| Analog  |                                                 |      |                                      |  |

| VDDA    | 1                                               | Р    | Analog power supply (2.3V ~ 3.6V)    |  |

| LNA_IN  | 2                                               | I/O  | RF input and output                  |  |

| VDDA3P3 | DDA3P3 3 P Power supply amplifier (2.3V ~ 3.6V) |      | Power supply amplifier (2.3V ~ 3.6V) |  |

| VDDA3P3 | 4                                               | Р    | Power supply amplifier (2.3V ~ 3.6V) |  |

| Name        | No. | Туре                                       | Function                                                 |  |

|-------------|-----|--------------------------------------------|----------------------------------------------------------|--|

|             |     |                                            | GPIO36, ADC_PRE_AMP, ADC1_CH0, RTC_GPIO0                 |  |

| SENSOR_VP   | 5   | 1                                          | Note: Connects a 270 pF capacitor from SENSOR_VP to SEN- |  |

|             |     |                                            | SOR_CAPP, when used as ADC_PRE_AMP.                      |  |

|             |     |                                            | GPIO37, ADC_PRE_AMP, ADC1_CH1, RTC_GPIO1                 |  |

| SENSOR_CAPP | 6   | 1                                          | Note: Connects a 270 pF capacitor from SENSOR_VP to SEN- |  |

|             |     |                                            | SOR_CAPP, when used as ADC_PRE_AMP.                      |  |

|             |     |                                            | GPIO38, ADC1 CH2, ADC PRE AMP, RTC GPIO2                 |  |

| SENSOR_CAPN | 7   | 1                                          | Note: Connects a 270 pF capacitor from SENSOR_VN to SEN- |  |

|             |     |                                            | SOR_CAPN, when used as ADC_PRE_AMP.                      |  |

|             |     |                                            | GPI039, ADC1_CH3, ADC_PRE_AMP, RTC_GPI03                 |  |

| SENSOR_VN   | 8   |                                            | Note: Connects a 270 pF capacitor from SENSOR_VN to SEN- |  |

| SENSON_VIV  | 0   | '                                          | SOR_CAPN, when used as ADC_PRE_AMP.                      |  |

|             |     |                                            | High: On; enables the chip                               |  |

| EN          | 9   |                                            |                                                          |  |

|             | 9   |                                            | Low: Off; resets the chip                                |  |

| 1004        | 10  |                                            | Note: Do not leave CHIP_PU pin floating.                 |  |

| IO34        | 10  |                                            | ADC1_CH6, RTC_GPI04                                      |  |

| IO35        | 11  | 1                                          | ADC1_CH7, RTC_GPI05                                      |  |

| IO32        | 12  | I/O                                        | 32K_XP (32.768 kHz crystal oscillator input), ADC1_CH4,  |  |

|             |     |                                            | TOUCH9, RTC_GPIO9                                        |  |

| 1033        | 13  | I/O                                        | 32K_XN (32.768 kHz crystal oscillator output), ADC1_CH5, |  |

|             |     |                                            | TOUCH8, RTC_GPIO8                                        |  |

| IO25        | 14  | I/O                                        | GPIO25, DAC_1, ADC2_CH8, RTC_GPIO6, EMAC_RXD0            |  |

| IO26        | 15  | I/O                                        | GPIO26, DAC_2, ADC2_CH9, RTC_GPIO7, EMAC_RXD1            |  |

| 1027        | 16  | I/O                                        | GPIO27, ADC2_CH7, TOUCH7, RTC_GPIO17, EMAC_RX_DV         |  |

| IO14        | 17  | I/O                                        | ADC2_CH6, TOUCH6, RTC_GPIO16, MTMS, HSPICLK,             |  |

| 1014        | 17  | 1/0                                        | HS2_CLK, SD_CLK, EMAC_TXD2                               |  |

| IO12        | 18  | I/O                                        | ADC2_CH5, TOUCH5, RTC_GPIO15, MTDI, HSPIQ,               |  |

| 1012        | 10  | 1/0                                        | HS2_DATA2, SD_DATA2, EMAC_TXD3                           |  |

| VDD3P3_RTC  | 19  | Р                                          | RTC IO power supply input (1.8V ~ 3.6V)                  |  |

| 1012        | 20  | 1/0                                        | ADC2_CH4, TOUCH4, RTC_GPIO14, MTCK, HSPID,               |  |

| IO13        | 20  | I/O                                        | HS2_DATA3, SD_DATA3, EMAC_RX_ER                          |  |

| 1015        | 01  | 1/0                                        | ADC2_CH3, TOUCH3, RTC_GPIO13, MTDO, HSPICS0,             |  |

| IO15        | 21  | I/O                                        | HS2_CMD, SD_CMD, EMAC_RXD3                               |  |

|             |     |                                            | ADC2_CH2, TOUCH2, RTC_GPIO12, HSPIWP, HS2_DATA0,         |  |

| 102         | 22  | I/O                                        | SD_DATA0                                                 |  |

|             |     |                                            | ADC2_CH1, TOUCH1, RTC_GPIO11, CLK_OUT1,                  |  |

| 100         | 23  | I/O                                        | EMAC_TX_CLK                                              |  |

|             |     |                                            | ADC2_CH0, TOUCH0, RTC_GPIO10, HSPIHD, HS2_DATA1,         |  |

| IO4         | 24  | I/O                                        | SD_DATA1, EMAC_TX_ER                                     |  |

| IO16        | 25  | I/O                                        | GPI016, HS1_DATA4, U2RXD, EMAC_CLK_OUT                   |  |

|             |     | Output power supply: 1.8V or the same volt |                                                          |  |

| VDD_SDIO    | 26  | P                                          | VDD3P3_RTC                                               |  |

| IO17        | 27  | I/O                                        | GPI017, HS1_DATA5, U2TXD, EMAC_CLK_OUT_180               |  |

| SD2         | 28  | 1/O                                        |                                                          |  |

| SD3         | 29  | 1/O                                        | GPI010, SD_DATA3, SPIWP, HS1_DATA3, U1TXD                |  |

| 000         | 23  | 1/0                                        |                                                          |  |

| Name                                              | No.        | Туре                                       | Function                                |

|---------------------------------------------------|------------|--------------------------------------------|-----------------------------------------|

| CMD                                               | 30         | I/O                                        | GPIO11, SD_CMD, SPICS0, HS1_CMD, U1RTS  |

| CLK                                               | 31         | I/O                                        | GPIO6, SD_CLK, SPICLK, HS1_CLK, U1CTS   |

| SD0                                               | 32         | I/O                                        | GPIO7, SD_DATA0, SPIQ, HS1_DATA0, U2RTS |

| SD1                                               | 33         | I/O                                        | GPIO8, SD_DATA1, SPID, HS1_DATA1, U2CTS |

| 105                                               | 34         | I/O                                        | GPIO5, VSPICS0, HS1_DATA6, EMAC_RX_CLK  |

| IO18                                              | 35         | I/O                                        | GPIO18, VSPICLK, HS1_DATA7              |

| IO23                                              | 36         | I/O                                        | GPIO23, VSPID, HS1_STROBE               |

| VDD3P3_CPU                                        | 37         | Р                                          | CPU IO power supply input (1.8V ~ 3.6V) |

| IO19                                              | 38         | I/O                                        | GPIO19, VSPIQ, UOCTS, EMAC_TXD0         |

| IO22                                              | 39         | I/O                                        | GPIO22, VSPIWP, UORTS, EMAC_TXD1        |

| UORXD                                             | 40         | I/O                                        | GPIO3, U0RXD, CLK_OUT2                  |

| U0TXD                                             | 41         | I/O                                        | GPIO1, U0TXD, CLK_OUT3, EMAC_RXD2       |

| IO21                                              | 42         | I/O                                        | GPIO21, VSPIHD, EMAC_TX_EN              |

| VDDA                                              | 43         | Р                                          | Analog power supply (2.3V ~ 3.6V)       |

| XTAL_N_NC                                         | 44         | -                                          | NC                                      |

| XTAL_P_NC                                         | 45         | -                                          | NC                                      |

| VDDA46PDigital power supply for PLL (2.3V ~ 3.6V) |            | Digital power supply for PLL (2.3V ~ 3.6V) |                                         |

| CAP2_NC                                           | NC 47 - NC |                                            | NC                                      |

| CAP1_NC                                           | 48         | -                                          | NC                                      |

#### Note:

Pins IO16, IO17, CMD, CLK, SD0 and SD1 are used for connecting the embedded flash, and are not recommended for other uses.

### 2.3 Strapping Pins

ESP32 has five strapping pins, which can be seen in Chapter 5 Schematics:

- MTDI

- GPI00

- GPIO2

- MTDO

- GPI05

Software can read the value of these five bits from the register "GPIO\_STRAPPING".

During the chip's system reset (power-on reset, RTC watchdog reset and brownout reset), the latches of the strapping pins sample the voltage level as strapping bits of "0" or "1", and hold these bits until the chip is powered down or shut down. The strapping bits configure the device boot mode, the operating voltage of VDD\_SDIO and other system initial settings.

Each strapping pin is connected with its internal pull-up/pull-down during the chip reset. Consequently, if a strapping pin is unconnected or the connected external circuit is high-impendence, the internal weak pull-up/pull-down will determine the default input level of the strapping pins.

To change the strapping bit values, users can apply the external pull-down/pull-up resistances, or apply the host MCU's GPIOs to control the voltage level of these pins when powering on ESP32.

After reset, the strapping pins work as the normal functions pins.

Refer to Table 3 for detailed boot modes' configuration by strapping pins.

#### **Table 3: Strapping Pins**

|       | Voltage of Internal LDO (VDD_SDIO) |                                      |                       |                     |                    |  |  |

|-------|------------------------------------|--------------------------------------|-----------------------|---------------------|--------------------|--|--|

| Pin   | Default                            | 3.                                   | 3V                    | 1.8                 | 8V                 |  |  |

| MTDI  | Pull-down                          | (                                    | )                     | -                   | 1                  |  |  |

|       |                                    |                                      | Booting Mode          |                     |                    |  |  |

| Pin   | Default                            | SPI                                  | Boot                  | Downlo              | ad Boot            |  |  |

| GPIO0 | Pull-up                            | -                                    | 1                     | (                   | )                  |  |  |

| GPIO2 | Pull-down                          | Don't                                | -care                 | (                   | )                  |  |  |

|       |                                    | Debugging Log                        | g Printed on U0TXD Du | ring Booting?       |                    |  |  |

| Pin   | Default                            | UOTXD                                | Toggling              | UOTXE               | ) Silent           |  |  |

| MTDO  | Pull-up                            | -                                    | 1                     | (                   | )                  |  |  |

|       |                                    |                                      | Timing of SDIO Slave  |                     |                    |  |  |

| Pin   | Default                            | Falling-edge Input                   | Falling-edge Input    | Rising-edge Input   | Rising-edge Input  |  |  |

| ГШ    | Delault                            | Falling-edge Output Rising-edge Outp |                       | Falling-edge Output | Rising-edge Output |  |  |

| MTDO  | Pull-up                            | 0                                    | 0                     | 1                   | 1                  |  |  |

| GPIO5 | Pull-up                            | 0                                    | 1                     | 0                   | 1                  |  |  |

Note:

Firmware can configure register bits to change the settings of "Voltage of Internal LDO (VDD\_SDIO)" and "Timing of SDIO Slave", after booting.

## 3. Functional Descriptions

This chapter describes the modules integrated in ESP32-PICO-D4, and their functions.

### 3.1 CPU and Internal Memory

ESP32 contains two low-power Xtensa® 32-bit LX6 microprocessors. The internal memory includes:

- 448 kB of ROM for booting and core functions.

- 520 kB (8 kB RTC FAST Memory included) of on-chip SRAM for data and instruction.

- 8 kB of SRAM in RTC, which is called RTC FAST Memory and can be used for data storage; it is accessed by the main CPU during RTC Boot from the Deep-sleep mode.

- 8 kB of SRAM in RTC, which is called RTC SLOW Memory and can be accessed by the co-processor during the Deep-sleep mode.

- 1 kbit of eFuse, of which 320 bits are used for the system (MAC address and chip configuration) and the remaining 704 bits are reserved for customer applications, including Flash-Encryption and Chip-ID.

### 3.2 External Flash and SRAM

ESP32 supports up to four 16-MB of external QSPI flash and SRAM with hardware encryption based on AES to protect developers' programs and data.

ESP32 can access the external QSPI flash and SRAM through high-speed caches.

- Up to 16 MB of external flash are memory-mapped onto the CPU code space, supporting 8, 16 and 32-bit access. Code execution is supported.

- Up to 8 MB of external flash/SRAM are memory-mapped onto the CPU data space, supporting 8, 16 and 32-bit access. Data-read is supported on the flash and SRAM. Data-write is supported on the SRAM.

The ESP32-PICO-D4 module integrates 4 MB of external SPI flash. The 4-MB SPI flash can be memory-mapped onto the CPU code space, supporting 8, 16 and 32-bit access. Code execution is supported.

#### Note:

The operating voltage of ESP32-PICO-D4's integrated external SPI flash is 3.3V. Therefore, the strapping pin MTDI should hold bit "0" during the module power-on reset.

### 3.3 Crystal Oscillators

ESP32-PICO-D4 integrates a 40 MHz crystal oscillator.

### 3.4 Peripherals and Sensors

#### Table 4: Description of Peripherals and Sensors

| Interface        | Signal    | Pin       | Function                                  |

|------------------|-----------|-----------|-------------------------------------------|

|                  | ADC1_CH0  | SENSOR_VP |                                           |

|                  | ADC1_CH3  | SENSOR_VN |                                           |

|                  | ADC1_CH4  | IO32      |                                           |

|                  | ADC1_CH5  | IO33      |                                           |

|                  | ADC1_CH6  | IO34      |                                           |

|                  | ADC1_CH7  | IO35      |                                           |

|                  | ADC2_CH0  | IO4       |                                           |

| ADC              | ADC2_CH1  | IO0       | Two 12-bit SAR ADCs                       |

|                  | ADC2_CH2  | 102       |                                           |

|                  | ADC2_CH3  | IO15      |                                           |

|                  | ADC2_CH4  | IO13      |                                           |

|                  | ADC2_CH5  | IO12      |                                           |

|                  | ADC2_CH6  | IO14      |                                           |

|                  | ADC2_CH7  | 1027      |                                           |

|                  | ADC2_CH8  | IO25      |                                           |

|                  | ADC2_CH9  | IO26      |                                           |

| DAC              | DAC_1     | IO25      | T 01/10 DAO                               |

|                  | DAC_2     | IO26      | - Two 8-bit DACs                          |

|                  | ТОИСНО    | 104       |                                           |

|                  | TOUCH1    | 100       |                                           |

|                  | TOUCH2    | 102       |                                           |

|                  | ТОИСНЗ    | IO15      |                                           |

| Touch Sensor     | TOUCH4    | IO13      | Capacitive touch sensors                  |

|                  | TOUCH5    | IO12      | Capacitive touch sensors                  |

|                  | TOUCH6    | IO14      |                                           |

|                  | TOUCH7    | IO27      |                                           |

|                  | TOUCH8    | IO33      |                                           |

|                  | TOUCH9    | IO32      |                                           |

|                  | HS2_CLK   | MTMS      |                                           |

|                  | HS2_CMD   | MTDO      |                                           |

| SD/SDIO/MMC Host | HS2_DATA0 | 102       | Currents CD memory courd V/0.01 star-doub |

| Controller       | HS2_DATA1 | 104       | Supports SD memory card V3.01 standard    |

|                  | HS2_DATA2 | MTDI      |                                           |

|                  | HS2_DATA3 | MTCK      |                                           |

| Interface | Signal             | Pin        | Function                                  |

|-----------|--------------------|------------|-------------------------------------------|

|           | PWM0_OUT0~2        |            |                                           |

|           | PWM1_OUT_IN0~2     |            | Three channels of 16-bit timers generate  |

|           | PWM0_FLT_IN0~2     |            | PWM waveforms. Each channel has a pair    |

| Motor PWM | PWM1_FLT_IN0~2     | Any GPIOs* | of output signals, three fault detection  |

|           | PWM0_CAP_IN0~2     |            | signals, three event-capture signals, and |

|           | PWM1_CAP_IN0~2     |            | three sync signals.                       |

|           | PWM0_SYNC_IN0~2    |            |                                           |

|           | PWM1_SYNC_IN0~2    |            |                                           |

| LED PWM   | ledc_hs_sig_out0~7 | Any GPIOs* | 16 independent channels @80 MHz           |

|           | ledc_ls_sig_out0~7 |            | clock/RTC CLK. Duty accuracy: 16 bits.    |

|           | U0RXD_in           |            |                                           |

|           | U0CTS_in           |            |                                           |

|           | U0DSR_in           |            |                                           |

|           | U0TXD_out          |            |                                           |

|           | UORTS_out          | Any GPIOs* |                                           |

|           | U0DTR_out          |            |                                           |

| UART      | U1RXD_in           |            | Two UART devices with hardware            |

|           | U1CTS_in           |            | flow-control and DMA                      |

|           | U1TXD_out          |            |                                           |

|           | U1RTS_out          |            |                                           |

|           | U2RXD_in           |            |                                           |

|           | U2CTS_in           |            |                                           |

|           | U2TXD_out          |            |                                           |

|           | U2RTS_out          |            |                                           |

|           | I2CEXT0_SCL_in     |            |                                           |

|           | I2CEXT0_SDA_in     |            |                                           |

|           | I2CEXT1_SCL_in     |            |                                           |

| 12C       | I2CEXT1_SDA_in     | Any GPIOs* | Two I2C devices in slave or master modes  |

|           | I2CEXT0_SCL_out    |            |                                           |

|           | I2CEXT0_SDA_out    |            |                                           |

|           | I2CEXT1_SCL_out    |            |                                           |

|           | I2CEXT1_SDA_out    |            |                                           |

| Interface         | Signal             | Pin        | Function                                                                      |  |

|-------------------|--------------------|------------|-------------------------------------------------------------------------------|--|

|                   | I2S0I_DATA_in0~15  |            |                                                                               |  |

|                   | I2S00_BCK_in       |            |                                                                               |  |

|                   | I2S0O_WS_in        |            |                                                                               |  |

|                   | I2S0I_BCK_in       | -          |                                                                               |  |

|                   | I2S0I_WS_in        | -          |                                                                               |  |

|                   | I2S0I_H_SYNC       |            |                                                                               |  |

|                   | I2S0I_V_SYNC       |            |                                                                               |  |

|                   | I2S0I_H_ENABLE     |            |                                                                               |  |

|                   | I2S0O_BCK_out      |            |                                                                               |  |

|                   | I2S0O_WS_out       |            |                                                                               |  |

|                   | I2S0I_BCK_out      | Any GPIOs* |                                                                               |  |

|                   | I2S0I_WS_out       |            | Stores input and output from to the output                                    |  |

| 12S               | I2SOO_DATA_out0~23 |            | Stereo input and output from/to the audio codec, and parallel LCD data output |  |

|                   | I2S1I_DATA_in0~15  |            |                                                                               |  |

|                   | I2S10_BCK_in       |            |                                                                               |  |

|                   | I2S10_WS_in        |            |                                                                               |  |

|                   | I2S1I_BCK_in       |            |                                                                               |  |

|                   | I2S1I_WS_in        |            |                                                                               |  |

|                   | I2S1I_H_SYNC       |            |                                                                               |  |

|                   | I2S1I_V_SYNC       |            |                                                                               |  |

|                   | I2S1I_H_ENABLE     |            |                                                                               |  |

|                   | I2S10_BCK_out      | -          |                                                                               |  |

|                   | I2S1O_WS_out       |            |                                                                               |  |

|                   | I2S1I_BCK_out      |            |                                                                               |  |

|                   | I2S1I_WS_out       |            |                                                                               |  |

|                   | I2S1O_DATA_out0~23 |            |                                                                               |  |

| Remote Controller | RMT_SIG_IN0~7      | Any GPIOs* | Eight channels of IR transmitter and                                          |  |

|                   | RMT_SIG_OUT0~7     |            | receiver for various waveforms                                                |  |

| Interface       | Signal           | Pin        | Function                                         |

|-----------------|------------------|------------|--------------------------------------------------|

|                 | SPIHD            | SHD/SD2    |                                                  |

|                 | SPIWP            | SWP/SD3    |                                                  |

|                 | SPICS0           | SCS/CMD    |                                                  |

|                 | SPICLK           | SCK/CLK    |                                                  |

|                 | SPIQ             | SDO/SD0    | _                                                |

|                 | SPID             | SDI/SD1    |                                                  |

|                 | HSPICLK          | IO14       |                                                  |

|                 | HSPICS0          | IO15       | Supports Standard SPI, Dual SPI, and             |

| Parallel QSPI   | HSPIQ            | IO12       | Quad SPI that can be connected to the            |

|                 | HSPID            | IO13       | external flash and SRAM                          |

|                 | HSPIHD           | IO4        | _                                                |

|                 | HSPIWP           | IO2        |                                                  |

|                 | VSPICLK          | IO18       |                                                  |

|                 | VSPICS0          | 105        |                                                  |

|                 | VSPIQ            | IO19       |                                                  |

|                 | VSPID            | IO23       |                                                  |

|                 | VSPIHD           | IO21       |                                                  |

|                 | VSPIWP           | IO22       |                                                  |

|                 | HSPIQ_in/_out    |            | Standard SPI consists of clock,                  |

|                 | HSPID_in/_out    |            | chip-select, MOSI and MISO. These SPIs           |

|                 | HSPICLK_in/_out  |            | can be connected to LCD and other                |

|                 | HSPI_CS0_in/_out |            | external devices. They support the               |

|                 | HSPI_CS1_out     |            | following features:                              |

| General Purpose | HSPI_CS2_out     | Any GPIOs* | <ul> <li>both master and slave modes;</li> </ul> |

| SPI             | VSPIQ_in/_out    | y          | 4 sub-modes of the SPI format                    |

|                 | VSPID_in/_out    |            | transfer that depend on the clock                |

|                 | VSPICLK_in/_out  |            | phase (CPHA) and clock polarity                  |

|                 | VSPI_CS0_in/_out |            | (CPOL) control;                                  |

|                 | VSPI_CS1_out     |            | • configurable SPI frequency;                    |

|                 | VSPI_CS2_out     |            | • up to 64 bytes of FIFO and DMA.                |

|                 | MTDI             | IO12       |                                                  |

| JTAG            | MTCK             | IO13       | JTAG for software debugging                      |

|                 | MTMS             | IO14       | o mailloi soltivale debugging                    |

|                 | MTDO             | IO15       |                                                  |

| Interface  | Signal           | Pin        | Function                             |

|------------|------------------|------------|--------------------------------------|

|            | SD_CLK           | IO6        |                                      |

|            | SD_CMD           | IO11       | SDIO interface that conforms to the  |

| SDIO Slave | SD_DATA0         | 107        | industry standard SDIO 2.0 card      |

|            | SD_DATA1         | IO8        | specification.                       |

|            | SD_DATA2         | IO9        |                                      |

|            | SD_DATA3         | IO10       |                                      |

|            | EMAC_TX_CLK      | IOO        |                                      |

|            | EMAC_RX_CLK      | IO5        |                                      |

|            | EMAC_TX_EN       | IO21       |                                      |

|            | EMAC_TXD0        | IO19       |                                      |

|            | EMAC_TXD1        | IO22       |                                      |

|            | EMAC_TXD2        | IO14       |                                      |

|            | EMAC_TXD3        | IO12       |                                      |

|            | EMAC_RX_ER       | IO13       |                                      |

|            | EMAC_RX_DV       | IO27       |                                      |

|            | EMAC_RXD0        | IO25       |                                      |

| EMAC       | EMAC_RXD1        | IO26       | Ethernet MAC with MII/RMII interface |

|            | EMAC_RXD2        | TXD0       |                                      |

|            | EMAC_RXD3        | IO15       |                                      |

|            | EMAC_CLK_OUT     | IO16       |                                      |

|            | EMAC_CLK_OUT_180 | IO17       |                                      |

|            | EMAC_TX_ER       | IO4        |                                      |

|            | EMAC_MDC_out     | Any GPIOs* |                                      |

|            | EMAC_MDI_in      | Any GPIOs* |                                      |

|            | EMAC_MDO_out     | Any GPIOs* |                                      |

|            | EMAC_CRS_out     | Any GPIOs* |                                      |

|            | EMAC_COL_out     | Any GPIOs* |                                      |

### 3.5 RTC and Power Consumption

With the use of advanced power management technologies, ESP32 can switch between different power modes.

- Power modes

- Active mode: The chip radio is powered on. The chip can receive, transmit, or listen.

- Modem-sleep mode: The CPU is operational and the clock is configurable. The Wi-Fi/Bluetooth baseband and radio are disabled.

- Light-sleep mode: The CPU is paused. The RTC memory and RTC peripherals, as well as the ULP co-processor are running. Any wake-up events (MAC, host, RTC timer, or external interrupts) will wake up the chip.

- Deep-sleep mode: Only the RTC memory and RTC peripherals are powered on. Wi-Fi and Bluetooth connection data are stored in the RTC memory. The ULP co-processor can work.

- Hibernation mode: The internal 8-MHz oscillator and ULP co-processor are disabled. The RTC recovery memory is powered down. Only one RTC timer on the slow clock and some RTC GPIOs are active.

The RTC timer or the RTC GPIOs can wake up the chip from the Hibernation mode.

The power consumption varies with different power modes/sleep patterns and work statuses of functional modules. Please see Table 5 for details.

| Power mode          | Description                                          | Power consumption                  |  |

|---------------------|------------------------------------------------------|------------------------------------|--|

|                     | Wi-Fi TX packet 14 dBm ~ 19.5 dBm                    |                                    |  |

| Active (RF working) | Wi-Fi / BT TX packet 0 dBm                           | Please refer to ESP32 Datasheet.   |  |

| Active (hr working) | Wi-Fi / BT RX and listening                          |                                    |  |

|                     | Association sleep pattern (by Light-sleep)           | 1 mA ~ 4 mA @DTIM3                 |  |

|                     |                                                      | Max speed 240 MHz: 30 mA ~ 50 mA   |  |

| Modem-sleep         | The CPU is powered on.                               | Normal speed 80 MHz: 20 mA ~ 25 mA |  |

|                     |                                                      | Slow speed 2 MHz: 2 mA ~ 4 mA      |  |

| Light-sleep         | -                                                    | 0.8 mA                             |  |

|                     | The ULP co-processor is powered on.                  | 150 μΑ                             |  |

| Deep-sleep          | ULP sensor-monitored pattern                         | 100 µA @1% duty                    |  |

|                     | RTC timer + RTC memory                               | 10 µA                              |  |

| Hibernation         | RTC timer only                                       | 5 µA                               |  |

| Power off           | CHIP_PU is set to low level, the chip is powered off | 0.1 μΑ                             |  |

#### Table 5: Power Consumption by Power Modes

#### Note:

- When Wi-Fi is enabled, the chip switches between Active and Modem-sleep mode. Therefore, power consumption changes accordingly.

- In Modem-sleep mode, the CPU frequency changes automatically. The frequency depends on the CPU load and the peripherals used.

- During Deep-sleep, when the ULP co-processor is powered on, peripherals such as GPIO and I2C are able to work.

- When the system works in the ULP sensor-monitored pattern, the ULP co-processor works with the ULP sensor periodically; ADC works with a duty cycle of 1%, so the power consumption is 100 μA.

## 4. Electrical Characteristics

#### Note:

The specifications in this chapter have been tested under the following general condition: VDD = 3.3V,  $T_A = 27^{\circ}$ C, unless otherwise specified.

### 4.1 Absolute Maximum Ratings

| Parameter                                    | Symbol           | Min                      | Тур | Max                               | Unit |

|----------------------------------------------|------------------|--------------------------|-----|-----------------------------------|------|

| Power supply                                 | VDD              | 2.7                      | 3.3 | 3.6                               | V    |

| Minimum current delivered by power supply    | I <sub>VDD</sub> | 0.5                      | -   | -                                 | А    |

| Input low voltage                            | V <sub>IL</sub>  | -0.3                     | -   | 0.25×V <sub>IO</sub> <sup>1</sup> | V    |

| Input high voltage                           | $V_{IH}$         | $0.75 \times V_{IO}^{1}$ | -   | V <sub>IO</sub> <sup>1</sup> +0.3 | V    |

| Input leakage current                        | $ _{IL}$         | -                        | -   | 50                                | nA   |

| Input pin capacitance                        | $C_{pad}$        | -                        | -   | 2                                 | pF   |

| Output low voltage                           | $V_{OL}$         | -                        | -   | $0.1 \times V_{IO}^{1}$           | V    |

| Output high voltage                          | $V_{OH}$         | $0.8 \times V_{IO}^{1}$  | -   | -                                 | V    |

| Maximum output drive capability              | $I_{MAX}$        | -                        | -   | 40                                | mA   |

| Storage temperature range $T_{STR}$          |                  | -40                      | -   | 85                                | °C   |

| Operating temperature range T <sub>OPR</sub> |                  | -40                      | -   | 85                                | °C   |

#### Table 6: Absolute Maximum Ratings

1. V<sub>IO</sub> is the power supply for a specific pad. More details can be found in the <u>ESP32 Datasheet</u>, Appendix IO\_MUX. For example, the power supply for SD\_CLK is the VDD\_SDIO.

### 4.2 Wi-Fi Radio

#### Table 7: Wi-Fi Radio Characteristics

| Description                      | Min      | Typical | Max  | Unit |

|----------------------------------|----------|---------|------|------|

| Input frequency                  | 2412     | -       | 2484 | MHz  |

| Output impedance                 | -        | 50      | -    | Ω    |

| Input reflection                 | -        | -       | -10  | dB   |

|                                  | Tx power |         |      |      |

| Output power of PA for 72.2 Mbps | 13       | 14      | 15   | dBm  |

| Output power of PA for 11b mode  | 19.5     | 20      | 20.5 | dBm  |

| Sensitivity                      |          |         |      |      |

| DSSS, 1 Mbps                     | -        | -98     | -    | dBm  |

| CCK, 11 Mbps                     | -        | -91     | -    | dBm  |

| OFDM, 6 Mbps                     | -        | -93     | -    | dBm  |

| OFDM, 54 Mbps                    | -        | -75     | -    | dBm  |

| HT20, MCS0                       | -        | -93     | -    | dBm  |

| Description                | Min | Typical | Max | Unit |  |

|----------------------------|-----|---------|-----|------|--|

| HT20, MCS7                 | -   | -73     | -   | dBm  |  |

| HT40, MCS0                 | -   | -90     | -   | dBm  |  |

| HT40, MCS7                 | -   | -70     | -   | dBm  |  |

| MCS32                      | -   | -89     | -   | dBm  |  |

| Adjacent channel rejection |     |         |     |      |  |

| OFDM, 6 Mbps               | -   | 37      | -   | dB   |  |

| OFDM, 54 Mbps              | -   | 21      | -   | dB   |  |

| HT20, MCS0                 | -   | 37      | -   | dB   |  |

| HT20, MCS7                 | -   | 20      | -   | dB   |  |

### 4.3 Bluetooth LE Radio

#### 4.3.1 Receiver

#### Parameter Conditions Min Тур Max Unit Sensitivity @30.8% PER -97 dBm --Maximum received signal @30.8% PER -0 -dBm Co-channel C/I -+10 dB -F = F0 + 1 MHz--5 dB F = FO - 1 MHz\_ -5 \_ dB F = F0 + 2 MHz-25 dB --Adjacent channel selectivity C/I F = F0 - 2 MHz-35 dB ---25 F = F0 + 3 MHzdB --F = F0 - 3 MHz\_ -45 dB 30 MHz ~ 2000 MHz -10 \_ dBm 2000 MHz ~ 2400 MHz -27 dBm -Out-of-band blocking performance 2500 MHz ~ 3000 MHz -27 dBm --3000 MHz ~ 12.5 GHz -10 -dBm Intermodulation -36 \_ \_ \_ dBm

#### Table 8: Receiver Characteristics – BLE

#### 4.3.2 Transmit

#### Table 9: Transmit Characteristics - BLE

| Parameter              | Conditions | Min | Тур | Max | Unit |

|------------------------|------------|-----|-----|-----|------|

| RF transmit power      | -          | -   | 0   | -   | dBm  |

| Gain control step      | -          | -   | ±3  | -   | dBm  |

| RF power control range | -          | -12 | -   | +12 | dBm  |

| Parameter                             | Conditions       | Min | Тур   | Max | Unit      |

|---------------------------------------|------------------|-----|-------|-----|-----------|

|                                       | F = F0 + 1 MHz   | -   | -14.6 | -   | dBm       |

|                                       | F = F0 - 1 MHz   | -   | -12.7 | -   | dBm       |

|                                       | F = F0 + 2 MHz   | -   | -44.3 | -   | dBm       |

| Adjacent channel transmit power       | F = F0 - 2 MHz   | -   | -38.7 | -   | dBm       |

| Adjacent channel transmit power       | F = F0 + 3 MHz   | -   | -49.2 | -   | dBm       |

|                                       | F = F0 - 3 MHz   | -   | -44.7 | -   | dBm       |

|                                       | F = F0 + > 3 MHz | -   | -50   | -   | dBm       |

|                                       | F = F0 - > 3 MHz | -   | -50   | -   | dBm       |

| $\Delta f 1_{avg}$                    | -                | -   | -     | 265 | kHz       |

| $\Delta f_{2\max}$                    | -                | 247 | -     | -   | kHz       |

| $\Delta f 2_{avg} / \Delta f 1_{avg}$ | -                | -   | -0.92 | -   | -         |

| ICFT                                  | -                | -   | -10   | -   | kHz       |

| Drift rate                            | -                | -   | 0.7   | -   | kHz/50 μs |

| Drift                                 | -                | -   | 2     | -   | kHz       |

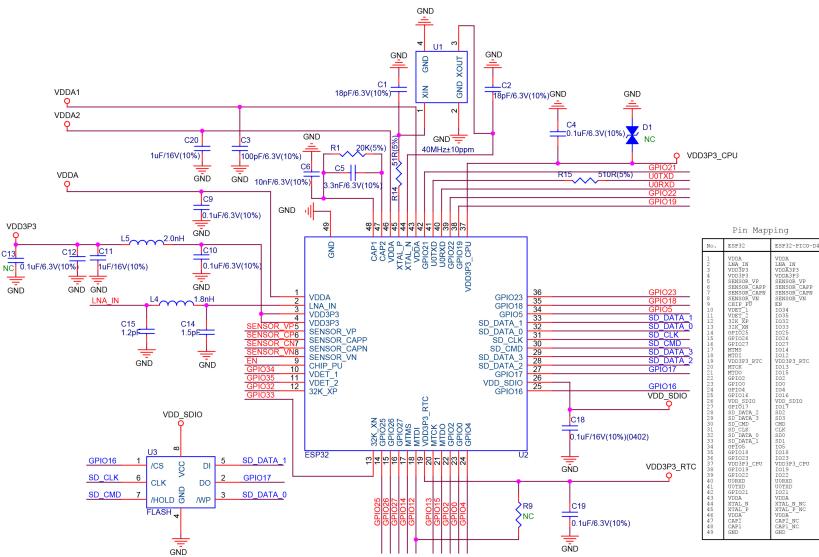

Figure 2: ESP32-PICO-D4 Module Schematics

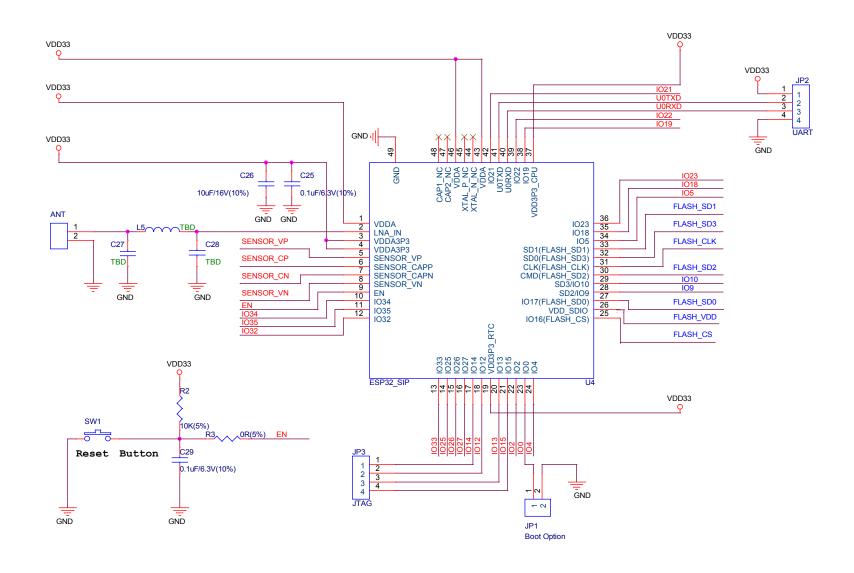

## 6. Peripheral Schematics

#### Note:

Soldering Pad 49 to the Ground of the base board is not necessary for a satisfactory thermal performance. If users do want to solder it, they need to ensure that the correct quantity of soldering paste is applied.

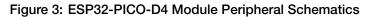

## 7. Package Information

H1

L

L1

е

b

\_\_\_

0.325

0.000

\_\_\_

0.200

0.300

0.400

0.075

0.500

0.250

---

0.013

0.000

\_\_\_

0.008

\_\_\_

0.475

0.150

\_\_\_

0.300

0.012

0.016

0.003

0.020

0.010

Side View

\_\_\_

0.019

0.006

\_\_\_

0.012

## 8. Learning Resources

### 8.1 Must-Read Documents

The following link provides documents related to ESP32.

• ESP32 Datasheet

This document provides an introduction to the specifications of the ESP32 hardware, including overview, pin definitions, functional description, peripheral interface, electrical characteristics, etc.

- ESP-IDF Programming Guide It hosts extensive documentation for ESP-IDF ranging from hardware guides to API reference.

- ESP32 Technical Reference Manual The manual provides detailed information on how to use the ESP32 memory and peripherals.

- ESP32 Hardware Resources

The zip files include the schematics, PCB layout, Gerber and BOM list of ESP32 modules and development boards.

• ESP32 Hardware Design Guidelines

The guidelines outline recommended design practices when developing standalone or add-on systems based on the ESP32 series of products, including ESP32, the ESP-WROOM-32 module, and ESP32-DevKitC—the development board.

• ESP32 AT Instruction Set and Examples

This document introduces the ESP32 AT commands, explains how to use them, and provides examples of several common AT commands.

Espressif Products Ordering Information

#### 8.2 Must-Have Resources

Here are the ESP32-related must-have resources.

• ESP32 BBS

This is an Engineer-to-Engineer (E2E) Community for ESP32 where you can post questions, share knowledge, explore ideas, and help solve problems with fellow engineers.

• ESP32 GitHub

ESP32 development projects are freely distributed under Espressif's MIT license on GitHub. It is established to help developers get started with ESP32 and foster innovation and the growth of general knowledge about the hardware and software surrounding ESP32 devices.

• ESP32 Tools

This is a webpage where users can download ESP32 Flash Download Tools and the zip file "ESP32 Certification and Test".

• ESP-IDF

This webpage links users to the official IoT development framework for ESP32.

ESP32 Resources

This webpage provides the links to all available ESP32 documents, SDK and tools.

## **Revision History**

| Date    | Version | Release notes                                               |

|---------|---------|-------------------------------------------------------------|

|         |         | Updated the pin description of VDD_SDIO in Section 2.2;     |

|         |         | Updated the ESP32-PICO-D4 Pin Layout in Section 2.1;        |

| 2018.03 | V1.2    | Updated the ESP32-PICO-D4 Module Schematics in Chapter 5;   |

|         |         | Updated the ESP32-PICO-D4 Module Peripheral Schematics in   |

|         |         | Chapter 6.                                                  |

| 2017.00 | \/+ +   | Operating voltage/power supply range updated to 2.7 ~ 3.6V; |

| 2017.09 | V1.1    | Added a note in Chapter 6.                                  |

| 2017.08 | V1.0    | First release.                                              |